主分类号: H01L 21/04(2006.01)

申请人: 富士电机株式会社

发明人: 河田泰之

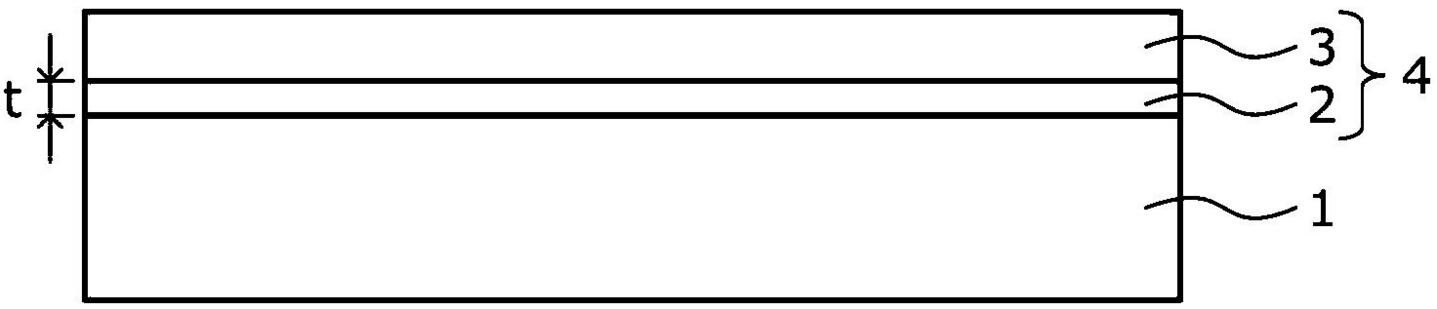

摘要: 本发明提供能够抑制碳化硅基板的表面缺陷的碳化硅半导体装置的制造方法。首先,在碳化硅基板1的离子注入面,形成依次层叠了硅膜2以及碳膜3的双层结构的保护膜4,进行活化热处理。硅膜2的厚度t为1nm以上且3nm以下。碳膜3的厚度为20nm以上。通过在活化热处理后除去碳膜3,进行其后的工序而在碳化硅基板1的离子注入面形成单元结构。在除去碳膜3后,使用XPS法以X射线入射角度45°分析碳化硅基板1的离子注入面的情况下,在碳化硅基板1的离子注入面,以使出现在结合能285eV~286eV的sp2键的碳的峰值强度相对于出现在结合能283eV~284eV的碳化硅的峰值强度的比值为0.4以下的方式设定保护膜厚度。

手机资讯

手机资讯 官方微信

官方微信

豫公网安备41019702003604号

豫公网安备41019702003604号